Scienxt Journal of Electrical Power System Volume-2 || Issue-1 || Jan-Apr || Year-2024 || pp. 25-36

# Analysis of multi-level inverter with limited device count for energy systems

## \*1Priyanshu Sahu, 2Namrata Sant, 3Vinay Pathak

\*1Department of Electrical & Electronics Engineering, Bhopal Institute of Technology,

Bhojpur Road Bhopal, 462045 M.P. India

2,3Student, Department of Electrical & Electronics Engineering,

Bhopal Institute of Technology, Bhojpur Road Bhopal, 462045 M.P. India

\*Corresponding Author: Priyanshu Sahu Email: pnpsahu2312@gmal.com

## **Abstract:**

In this study, a new multilevel converter topology is suggested. The suggested topology's key characteristics are its low component count and compact design. The suggested converter also lacks capacitors, inductors, and diodes, which allows for a smaller converter footprint, longer converter lifetime, and easier control method. In addition, a comparison with current multilevel topologies is done to illustrate the advantages of the proposed circuit. A presentation of the simulation results for the three-level version utilising various modulation schemes follows.

## **Keywords:**

Pulse width modulation multilevel inverters, fundamental frequency modulation, THD

## 1. Introduction:

In order to meet the rising demand for energy around the world while limiting CO<sub>2</sub> emissions, renewable energy generators (REGs) are becoming more heavily incorporated into the grid. As a result, considerable reductions in CO<sub>2</sub> emissions and notable advancements in energy saving are made. To improve system dependability and effectiveness, however, new technological proposals are constantly needed. The requirement for better power electronics converters (PECs), which connect the primary energy source to the grid, has increased as a result of recent advancements in those technologies. In power systems with renewable generators, PECs are crucial because they transform the generated primary power from REGs to be in compliance with the grid or load regulations. PECs are also used to improve the efficiency of generating systems due to their capacity to integrate various storage technologies, which enables them to perform a number of crucial tasks like energy arbitrage, peak shaving, load-flowing, spinning reserves, voltage support, black starts, frequency regulation, etc. [1].

Photovoltaic (PV), wind, and hydropower plants (HPP) are the main types of REGs. Different converter families, including conventional voltage source converters (VSCs), matrix converters (MCs), and cyclo-converters (CCVs), have been utilised in these generating systems for a very long period. However, significant issues with these converters include limited power handling caused by the maximum power ratings of semiconductor devices that are currently available, high total harmonic distortion (THD) on the input and output sides, and a negative impact on the system's power factor when using converters that are not fully controlled, like CCV [2-5]. For the purpose of overcoming the aforementioned restrictions, a number of solutions have been put forth, including the use of identical converters in parallel configurations to increase the handled power, the use of elaborate, large, and specially designed filters to improve THD, and the use of compensation circuits to control reactive power and enhance power factor in converters that are not fully controlled. However, these approaches are currently losing their appeal because they make PECs heavier, more complex, and more expensive, while also reducing the effectiveness, dependability, and lifespan of the energy system [2, 3, 5]. These limitations stop these converters from being used in high power applications. Multilevel converters (MLCs) are employed extensively in contemporary medium- and high-power energy systems because to their special characteristics of modularity, low dv/dt, low THD, low switching frequency, low electromagnetic interferences, minimal filtering requirements, and low switching losses [6-8]. Or to put it another way, systems based on MLCs generate highquality outputs with manageable side effects.

Three typical topologies of MLCs are the cascaded H-bridge converter (CHB) [13], the flying capacitors converter (FC) [11, 12], and the neutral point clamped converter (NPC) [9, 10]. The fundamental disadvantage of the aforementioned topologies is their high component count, which includes DC sources, electrolytic capacitors, transformers, switching devices, and power diodes. This increases the footprint, cost, conduction losses, control complexity, and lifetime of the converter [6-8]. A number of topologies were recently given in [14-20] with the intention of improving traditional setups by recommending new circuits with fewer components and easier control methods. This research proposes a new multilevel converter topology with this objective in mind. In comparison to the current setups, the proposed architecture can generate the same number of voltage levels with a less component count. The proposed topology also offers a compact design feature since it doesn't operate by using electrolytic capacitors or transformers. This portable solution's small size and minimal cooling system requirements are made possible by this feature's compactness. Additionally, the suggested circuit's losses will be drastically reduced because it uses solely switching devices that operate at low frequencies rather than hybrid designs that combine switches and diodes.

The structure of this essay is as follows. In part II, the proposed topology's operational principles for a three-level setup will be provided. The suggested circuit will be compared to various MLC topologies for producing the same number of voltage levels in section III. Then, part IV will discuss the two switching techniques that have been used, and section V will present the outcomes of the simulations for the two modulation techniques. In section VI, conclusions will be retracted.

## 2. Proposed multi-level converter topology:

Designing the proposed MLC topology had as its primary goal the simplification of the converter construction. This allows for the adoption of a straightforward control system and increases reliability to a greater extent. In order to avoid enlarging the converter's size, incurring losses, or shortening its lifetime, the design of the suggested topology shouldn't include electrolytic capacitors, power transformers, or power diodes. Additionally, the input DC ports need to be shrunk for larger applications. Therefore, fewer isolated DC sources will be needed, which will save costs. Typically, a six-pulse rectifier and an isolation transformer define one DC source. Saving one DC source translates into saving six power diodes and one isolation transformer, respectively. This viewpoint claims that the suggested topology is built to have fewer isolated DC sources while maintaining a manageable switching device count. The

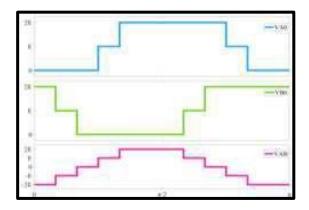

suggested design generates three-level pole voltages from just two DC sources and twelve switching devices, culminating in five-level line voltages. For instance, two PV generators can be used to create the two isolated DC sources. The suggested MLC's power circuit and consequent voltages are shown in Fig. 1. Even though the proposed topology can be expanded to N levels, this work only studies the three-level setup.

Pole voltage will be used to refer to the voltage differential between point A, B, or C and point 0 throughout this essay. Both line and phase voltages can be synthesised using the pole voltages VA0, VB0, and VC0. In order to produce three-level voltage waveforms with 120° phase shifts, both switching techniques are built to control the switches that are used. As a result, it is possible to create five-level line voltages, as demonstrated in Fig. 1, where the line voltage VAB is created by deducting VA0 from VB0.

Figure. 1: Line voltage VAB synthesization using pole voltages VA0 and VB0

## 3. Comparison of the proposed topology with other MLC topologies:

As indicated in section I, conventional multi-level converters like the CHB, FC, and NPC suffer from a number of control and component count issues. New and modified topologies have been documented in [14-20] to get around these restrictions. These topologies seek to reduce the number of components while boosting effectiveness and dependability. Despite the fact that these configurations are frequently utilised in industrial applications, some of them are still undergoing research and development. The findings of a comparison technique about the components necessary to generate an equivalent number of voltage levels are summarised in Table I. The following unified restrictions form the foundation of the comparative strategy: generating three-level pole voltages for each topology while only employing symmetrical DC sources, i.e. counting a DC voltage source with a rating of 2E as two separate DC sources, and converting single-phase topologies into three-phase versions before comparison. In terms of the component count at the same voltage levels and the given limitations, Table. I compares the proposed topology to known circuits in the literature. Comparing the suggested architecture to

the existing three-level topologies, it may provide the same output voltage levels while utilising less components. The absence of capacitors, diodes, and inductors is the suggested topology's key benefit, as it enables the proposed MLC to have a longer lifespan, lower switching losses, and a compact design. The next paragraphs emphasise and describe the primary traits and constraints of the comparative topologies.

A three-level topology was introduced which is an expansion of the split- source inverter (SSI) with two levels that was described. It has a boosting feature that enables it to provide a high-quality three-level output voltage, facilitating the direct connection of low-voltage energy sources like photovoltaics (PV). One DC supply, twelve semiconductor switches, three power diodes, four capacitors, and just one inductor are needed to generate three levels. Although this topology has features like multi-level outputs, boosting capability, and operating with a single source, it has drawbacks like high current and voltage stresses on the used semiconductor components, a limited capacity for power transfer, an increased system footprint due to capacitors and inductors, increased control complexity due to these components, and a shorter expected lifetime of the converter.

Table. 1: Comparison between the proposed topology and three-level

| Topology                         | DC<br>Sources | Switch<br>es | Diodes | Capacito<br>rs | Ind<br>ctors | Total | CLF |

|----------------------------------|---------------|--------------|--------|----------------|--------------|-------|-----|

| Modified T-type [19]             | 1             | 9            | 12     | 2              | 0            | 24    | 8.0 |

| Fig. 8 in [16]                   | 3             | 9            | 9      | 0              | 3            | 24    | 8.0 |

| In [18]                          | 1             | 18           | 0      | 3              | 0            | 22    | 7.3 |

| Neutral point clamped (NPC)      | 1             | 12           | 6      | 2              | 0            | 21    | 7.0 |

| Active T-type converter [14, 17] | 1             | 18           | 0      | 2              | 0            | 21    | 7.0 |

| In [20]                          | 1             | 12           | 3      | 4              | 1            | 21    | 7.0 |

| Cascaded half H-Bridge (CHHB)    | 6             | 12           | 0      | 0              | 0            | 18    | 6.0 |

| Flying capacitors (FCs)          | 1             | 12           | 0      | 4              | 0            | 17    | 5.7 |

| Cascaded full H-bridge (CHB)     | 3             | 12           | 0      | 0              | 0            | 15    | 5.0 |

| T-type converter [14, 19]        | 1             | 12           | 0      | 2              | 0            | 15    | 5.0 |

| Fig. 5 in [15]                   | 3             | 9            | 3      | 0              | 0            | 15    | 5.0 |

| The proposed topology            | 2             | 12           | 0      | 0              | 0            | 14    | 4.7 |

Additionally, the output voltage's quality depends on the gain value; for example, for low input voltages, increasing the output voltage causes a rise in THD. Additionally, it requires additional work in the control algorithms to eliminate the low-frequency components brought on by oscillations in the voltages of flying capacitors, both in the input current and the output voltage. Additionally, in grid-connected mode, using soft- start-up resistors is required to limit switch voltage stress during startup, while in stand- alone mode, controlling these issues can be done in part by setting control parameters in the control algorithm.

Authors in [18] have highlighted a new MLC that uses multiple sets of anti-parallel switches for the level-generator stages in addition to two primary switches to adjust the polarity of the output voltages. This configuration needs 18 switches, 3 capacitors, and 1 DC source to generate three-level three-phase voltage. The main drawbacks of this circuit include the use of electrolytic capacitors to divide a single DC source into three equal parts, the necessity of a large number of switches, and high voltage stress across switches used to change polarity, which causes a variety of losses and heat distribution inside the converter. As a result, the system lifetime is shortened while the converter cost, size, losses, and control complexity rise.

In [15], a dual-DC-port asymmetrical MLI (DPAMLI) was created and studied. To produce three-level voltage for three-phase applications, nine switches, three power diodes, and three DC sources (two with E and one with 2E) are needed. For the purpose of deriving the proposed topology, the neutral point clamped (NPC) and T-type three- level cells are utilised. Despite the fact that the DPMLI can support bidirectional power flow between input and output ports, only a unidirectional version was highlighted and confirmed in [15] with the intention of lowering the number of components. It is a single-stage converter that can be used to connect two DC sources of various ratings and can generate AC output voltages with several levels. This facilitates and improves the efficiency of connecting several voltage sources to a single converter. It has two operating modes, and the controller chooses one of them depending on how much voltage is actually delivered across the low DC port terminals in proportion to the needed output voltage. Although it has no issues using electrolytic capacitors, it also employs power diodes, which increases converter losses. This topology can only be used in low- and medium-voltage systems since at least six switches have high voltage stresses equal to the voltage delivered across the high-voltage DC port terminals.

The authors of [19] have developed a modified three-level topology of the well- known T-type MLI with the aim of reducing switch count. A cell made up of one switch and four diodes was used in place of the three bidirectional switches that connected the load points and the clamped

neutral point. Two capacitors, one DC source, twelve power diodes, nine switches, and a typical T-type architecture are required for this topology to produce the same output voltage levels. For many applications that need great efficiency, durability, and small size, this topology is unappealing due to the use of capacitors and a significant number of semiconductor components.

## 4. Simulation results and discussions:

A three-level model is created and simulated for both a pulse width modulation technique and a fundamental frequency modulation in order to demonstrate the operation of the suggested architecture. To provide a three-level pole voltage, the simulated model employs twelve switches (nine of E volt and three of 2E volt) and two symmetrical DC voltage sources. The primary simulation settings are provided in Table II, and the simulation results were obtained using the PSIM software.

System parametersValueDC voltage value E100 VLoad value at 50 Hz $R=50 \Omega, XL=23.6 \Omega$ Switching Frequency Fs2.5. KHzModulation index Mi (= SinM / CRM)1

Table. 2: Simulations system main specifications

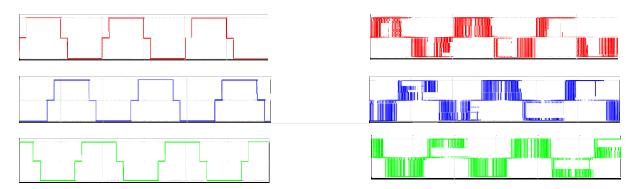

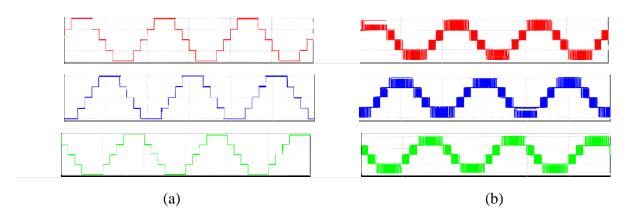

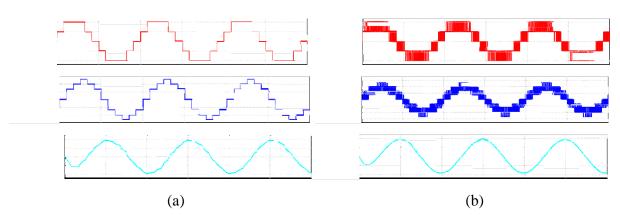

When the suggested converters are modulated by SCM and LSPWM switching techniques, the pole voltages VA0, VB0, and VC0 are shown in Fig. 2. Five-level balanced three-phase line voltages VAB, VBC, and VCA will be produced at the load terminals by maintaining the voltage across pole terminals have three steps and a phase shift of 120°, as illustrated in Fig. 3. The simulation results for the suggested topology when powering a resistive-inductive load with a power factor of 0.9 are shown in Fig. 4.

It can be seen that the voltage level number differs between the two graphs for VAN in Fig. 4(a) and (b), which is compatible with the used switching strategy. There are nine levels of -4/3 E, - E, -2/3 E, -1/3 E, 0, 1/3 E, 2/3 E, E, 4/3 E for LSPWM and seven levels of -4/3 E, - E, -2/3 E, 0, 2/3 E, E, 4/3 E for SCM in VAN. When adopting the LSPWM switching scheme, two new voltage combinations in the pole voltages result in the generation of the two additional voltage

levels in VAN 1/3 E. More information on the impact of switching strategies on the phase voltage level number is given in Table.3.

Figure. 2: The pole voltage waveforms: VA0, VB0, and VC0. (a) Staircases modulation. (b) Level-shifted PWM

Figure. 3: The output line voltage waveforms: VAB, VBC, and VCA. (a) Staircases modulation Level-shifted PWM

Figure. 4: The output waveforms under R-L load: VAB, VAn, and IAn. (a) Staircases modulation. (b) Levelshifted PWM

#### 5. Conclusion:

In this work, a brand-new three-level multilevel inverter is suggested and examined. Without the use of any passive components, the suggested topology is capable of producing a three-level pole voltage. In comparison to other three-level topologies that are already in use, it also requires less components. For the purpose of creating three balanced three-phase output voltages, two modulation techniques based on fundamental frequency modulation and sinusoidal pulse width modulation are successfully used. A simulation model of the circuit and the resistive-inductive load is used to confirm the effectiveness of the suggested topology. Additionally, a comparison study is conducted to demonstrate the benefits of the suggested circuit, offer insight into the trade-offs in design, and determine the best multilevel converter topologies.

## 6. References:

- (1) M. Faisal, M. A. Hannan, P. J. Ker, A. Hussain, M. B. Mansor, and F. Blaabjerg, "Review of Energy Storage System Technologies in Microgrid Applications: Issues and Challenges," IEEE Access, vol. 6, pp. 35143-35164, 2018.

- (2) M. V. Pronin, O. B. Shonin, A. G. Vorontsov, and G. A. Gogolev, "Features of a drive system for pump-storage plant applications based on the use of double-fed induction machine with a multistage-multilevel frequency converter," in 2012 15th International Power Electronics and Motion Control Conference (EPE/PEMC), 2012, pp. DS1b.7-1-DS1b.7-8.

- (3) J. Janning and A. Schwery, "Next generation variable speed pump-storage power stations," in 2009 13th European Conference on Power Electronics and Applications, 2009, pp. 1-10.

- (4) M. Pronin, O. Shonin, A. Vorontsov, and G. Gogolev, "A pumped storage power plant with double-fed induction machine and cascaded frequency converter," in Proceedings of the 2011, 14th European Conference on Power Electronics and Applications, 2011, pp. 1-9.

- (5) A. Joseph and T. R. Chelliah, "A Review of Power Electronic Converters for Variable Speed Pumped Storage Plants: Configurations, Operational Challenges, and Future Scopes," IEEE Journal of Emerging and Selected Topics in Power Electronics, vol. 6, no. 1, pp. 103-119, 2018.

- (6) A. Dekka, B. Wu, R. L. Fuentes, M. Perez, and N. R. Zargari, "Evolution of Topologies, Modeling, Control Schemes, and Applications of Modular Multilevel Converters," IEEE Journal of Emerging and Selected Topics in Power Electronics, vol. 5, no. 4, pp. 1631-1656, 2017.

- (7) H. Akagi, "Multilevel Converters: Fundamental Circuits and Systems," Proceedings of the IEEE, vol. 105, no. 11, pp. 2048-2065, 2017.

- (8) S. Debnath, J. Qin, B. Bahrani, M. Saeedifard, and P. Barbosa, "Operation, Control, and Applications of the Modular Multilevel Converter: A Review," IEEE Transactions on Power Electronics, vol. 30, no. 1, pp. 37-53, 2015.

- (9) R. H. Baker, "Switching circuit," ed: Google Patents, 1980.

- (10) A. Nabae, I. Takahashi, and H. Akagi, "A New Neutral-Point-Clamped PWM Inverter," IEEE Transactions on Industry Applications, vol. IA-17, no. 5, pp. 518- 523, 1981.

- (11) T. A. Meynard and H. Foch, "Multi-level conversion: high voltage choppers and voltage-source inverters," in PESC '92 Record. 23rd Annual IEEE Power Electronics Specialists Conference, 1992, pp. 397-403 vol.1.

- (12) J.-P. Lavieville, P. Carrere, and T. Meynard, "Electronic circuit for converting electrical energy, and a power supply installation making use thereof," ed: Google Patents, 1997.

- (13) R. H. Baker and L. H. Bannister, "Electric power converter," ed: Google Patents, 1975.

- (14) Y. Wang, W. W. Shi, N. Xie, and C. M. Wang, "Diode-Free T-Type Three-Level Neutral-Point-Clamped Inverter for Low-Voltage Renewable Energy System," IEEE Transactions on Industrial Electronics, vol. 61, no. 11, pp. 6168-6174, 2014.

- (15) H. Wu, L. Zhu, F. Yang, T. Mu, and H. Ge, "Dual-DC-Port Asymmetrical Multilevel Inverters With Reduced Conversion Stages and Enhanced Conversion Efficiency," IEEE Transactions on Industrial Electronics, vol. 64, no. 3, pp. 2081- 2091, 2017.

- (16) F. Yang, H. Ge, J. Yang, R. Dang, and H. Wu, "A Family of Dual-Buck Inverters With an Extended Low-Voltage DC-Input Port for Efficiency Improvement Based on Dual-Input Pulsating Voltage-Source Cells," IEEE Transactions on Power Electronics, vol. 33, no. 4, pp. 3115-3128, 2018.

- (17) R. Katebi, J. He, and N. Weise, "Investigation of Fault-Tolerant Capabilities in an Advanced Three-Level Active T-Type Converter," IEEE Journal of Emerging and Selected Topics in Power Electronics, vol. 7, no. 1, pp. 446-457, 2019.

- (18) R. G. Ganesan, M. Bhaskar, and K. Narayanan, "Novel 11-level Multi-level Inverter," in 2018 IEEE Innovative Smart Grid Technologies Asia (ISGT Asia), 2018, pp. 1050-1055.

- (19) C. L. Solanki, M. H. Ayalani, and S. N. Gohil, "Performance of Three Phase T- Type Multilevel Inverter with Reduced Switch Count," in 2018 International Conference on Current Trends towards Converging Technologies (ICCTCT), 2018, pp. 1-5.

Table. 3: The switching modulation effects on the number of levels of the phase voltage van

|     | VA0   |     | VB0   |     | VC0   |        | VAN    |

|-----|-------|-----|-------|-----|-------|--------|--------|

| SCM | LSPWM | SCM | LSPWM | SCM | LSPWM | SCM    | LSPWM  |

| 2E  | 2E    | 0   | 0     | 0   | 0     | 4/3 E  | 4/3 E  |

| 2E  | 2E    | Е   | Е     | 0   | 0     | E      | Е      |

| 2E  | 2E    | 2E  | Е     | 0   | Е     | 2/3 E  | 2/3 E  |

| -   | Е     | -   | Е     | -   | 0     | -      | 1/3 E  |

| Е   | Е     | 2E  | 2E    | 0   | 0     | 0      | 0      |

| -   | Е     | -   | 2E    | -   | Е     | -      | -1/3 E |

| 0   | 0     | 2E  | 2E    | 0   | 0     | -2/3 E | -2/3 E |

| 0   | 0     | 2E  | 2E    | Е   | Е     | -E     | -E     |

| 0   | 0     | 2E  | 2E    | 2E  | 2E    | -4/3 E | -4/3 E |